# **Evaluation Board Documentation AD7751/AD7755 Energy Metering IC**

# **EVAL-AD7751/AD7755EB**

#### **FEATURES**

Single +5 V Power Supply

Easy Connection of External Transducers via Screw Terminals

Easy Modification of Signal Conditioning Components Using PCB Sockets

Trim Pot for Analog Calibration of Meter Constant LED Indicators on Logic Outputs for Fault (AD7751 Only), REVP and CF

Optically Isolated Output for Calibration/Test Purposes External Reference Option Available for Reference Evaluation

#### GENERAL DESCRIPTION

The AD7751 and AD7755 are high accuracy energy measurement ICs. The part specifications surpass the accuracy requirements as quoted in the IEC1036 standard. The AD7751 incorporates a novel fault detection scheme that both warns of fault conditions with the logic output FAULT but allows the AD7751 to continue accurate billing during a fault event. The AD7751 does this by continuously monitoring both the phase and neutral (return) currents. A fault is indicated when these currents differ

by more than 12.5%. Billing is continued using the larger of the two currents. The FAULT output is connected to an LED on the evaluation board.

The AD7751 supplies average real power information on the low frequency outputs F1 and F2. These logic outputs may be used to directly drive an electromechanical counter or interface to an MCU. The evaluation board provides screw connectors for easy connection to an external counter. The CF logic output gives instantaneous real power information. This output is intended to be used for calibration purposes. The evaluation board allows this logic output to be connected to an LED or optoisolator. The REVP logic output goes high when negative real power is detected. This causes an LED on the evaluation board to switch on.

The AD7751/AD7755 evaluation board can easily be converted into an energy meter by the addition of a local power supply and the connection of the appropriate transducers. A large amount of prototype area is made available on the evaluation board for this purpose.

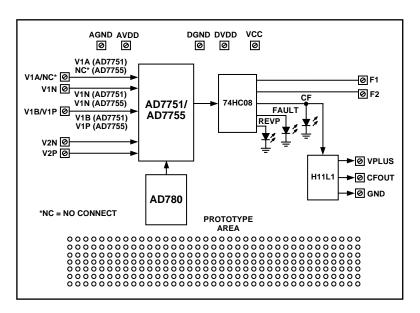

#### FUNCTIONAL BLOCK DIAGRAM

#### **ANALOG INPUTS (SK1 AND SK2)**

Voltage and current signals are connected at the screw terminals SK1 and SK2 respectively. All analog input signals are filtered using the on-board antialias filters before being presented to the analog inputs of the AD7751 or AD7755. Some analog inputs offer additional signal conditioning, e.g., attenuation on the voltage channel. The default component values shipped with the evaluation board are the recommended values to be used with the AD7751 and AD7755. The user can easily change these components, however this is not recommended unless the user is familiar with sigma-delta converters and also the criteria used for selecting the analog input filters—see AD7751 and AD7755 data sheets.

#### Voltage Input

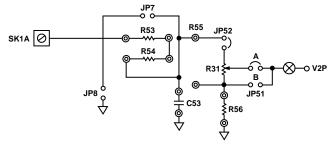

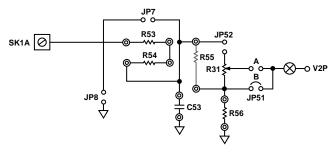

SK1 is a two-way connection block that can be directly connected to a high voltage source, e.g., 220 V rms. The resistor network R53, R54, R55, R56 and R31 make up a very flexible attenuation and calibration network—see schematic. The attenuation network is designed such that the corner frequency (–3 dB frequency) of the network matches that of the RC (antialiasing) filters on the other analog inputs. This is important, because if they do not match there will be large errors at low power factors. Figure 1 shows how the attenuation network may be used with fixed resistors or the trim pot. The trim pot allows the voltage signal on V2P to be scaled to calibrate the frequency on CF to some given constant, e.g., 3200 imp/kWhr. Some examples are given later.

a. Attenuation Using Trim Pot (R31)

b. Attenuation Using Fixed Resistors Figure 1. Attenuation Network on Channel 2

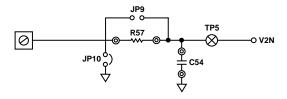

If Channel 2 is being used in a single-ended mode of operation, the unused input of the pair should be connected to analog ground (AGND) via an antialias filter. This is shown in Figure 2 where V2N is connected to AGND using jumper JP10.

Figure 2. Unused Analog Inputs Connected to AGND

All passive components (resistors and capacitors) which make up the attenuation network and antialias filters may be modified by the user. The components at mounted using PCB jack sockets which allow for easy removal and replacement of components.

#### **Current Input**

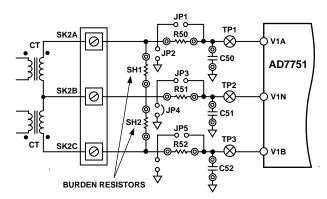

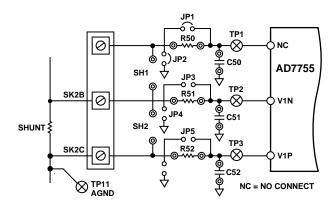

SK2 is a three-way connection block which allows the AD7751/AD7755 to be connected to a current transducer. The AD7751 has three inputs which are used with two current transducers, e.g., two CTs (current transformers). The AD7755 has one differential input channel for connection to the current transducer, i.e., two inputs. When using the AD7755 in the evaluation board the input SK2A is not used. PCB jack sockets allow CT burden resistors to be placed on the evaluation board at positions SH1 and SH2. Figures 3 and 4 show some typical connection diagrams for CT and shunt connection.

Figure 3. Typical Connection for Channel 1 of the AD7751

Figure 4. Typical Connection for Channel 1 of the AD7755

-2- REV. 0

#### AD7751/AD7755 EVALUATION BOARD SETUP

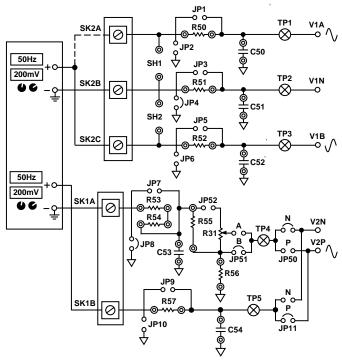

Figure 5 shows how the AD7751/AD7755 evaluation board can be set up for a simple evaluation. Two signal generators are used to provide the sinusoidal (ac) signals for Channel 1 and Channel 2. The user must have some way of phase locking the generators. This will ensure that the sinusoidal signals remain in phase. Also if the AD7751 and AD7755 performance-over-power factor is being evaluated, two separate signal sources will be required. The generators are shown connected in a single-ended configuration. The grounded analog inputs of Channel 1 and Channel 2 (V1N and V2N) are connected to AGND via an antialias filter. In Figure 5, analog input V2N is grounded via R55 and R56. The capacitor C53 is connected in parallel.

Figure 5. Typical Connection for Analog Inputs

#### LOGIC OUTPUTS

AD7751 and AD7755 provide the active power information in the form of an output frequency. The three frequency outputs are F1, F2 and CF. Consult the AD7751 and AD7755 data sheets for more information on these outputs. The logic outputs F1 and F2 are intended to be used to drive an impulse counter or stepper motor. The outputs are buffered and available at the connector SK6. A stepper motor may be directly connected here. The power supply for the buffer is VCC (SK4A) and may be connected to either the AD7751/AD7755 supply using jumper JP21, or to its own supply.

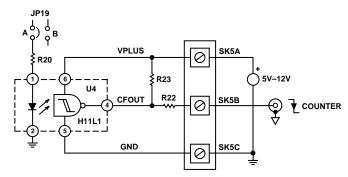

The logic output CF can be directly connected to an LED using JP19 (Position B) or to an optically isolated output (Position A). By closing Positions A and B, both options are selected. The optically isolated output is available at connector SK5. This isolated output is useful when the evaluation board is connected directly to a high voltage (e.g., 220 V residential). A typical connection diagram for this isolated output is shown in Figure 6.

Figure 6. Typical Connection for Opto Output

The logic output REVP indicates negative power measurement. Since the frequency outputs can only convey magnitude information, the sign of the power calculation is given by the REVP logic output. For more information regarding this output see the AD7751/AD7755 data sheet. This output is connected to an LED on the evaluation board. The LED will be illuminated if negative power is detected.

The AD7751 also has a logic output called FAULT. This output goes active when the signal levels on V1A and V1B differ by more than 12.5% (see Figure 3). This output is also connected to an LED on the evaluation board. Jumper J22 should be open when evaluating the AD7751.

All logic outputs can be monitored via test points 6 to 10 (TP6 to TP10). These test points provide easy access for scope probes and meter probes.

REV. 0 –3–

#### AD7751/AD7755 OUTPUT FREQUENCY SELECTION

AD7751 and AD7755 provide up to four different output frequencies on F1 and F2. The output frequency selection is made via the logic inputs S0 and S1—see AD7751/AD7755 data sheet. On the evaluation board these inputs are set by using jumpers JP15 and JP16. The logic input SCF is set via jumper 14 (JP14). For a full explanation of the AD7751/AD7755 output frequency selection see the data sheet.

#### AD7751/AD7755 INPUT GAIN SELECTION

AD7751 and AD7755 provide up to four different gain settings on the analog input Channel 1. These gain settings are 1, 2, 8 and 16. The gain selection on the evaluation board is made via JP17 and JP18.

#### **EXTERNAL CLOCK INPUT**

AD7751 and AD7755 are specified with a CLKIN value of 3.579545 MHz. The evaluation board uses a crystal of this value for the on-chip gate oscillator circuit. However, an input is provided to allow an external clock source to be used. An impedance matching resistor (R11) of 50  $\Omega$  is also available on the board. NOTE: when using the on-chip oscillator this resistor must be removed or the on-chip oscillator circuit will not start up.

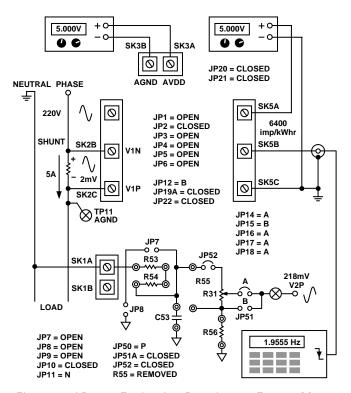

Figure 7. AD7755 Evaluation Board as an Energy Meter

# AD7755 EVALUATION BOARD SET UP AS AN ENERGY METER

Figure 7 shows a wiring diagram that allows a simple energy meter to be implemented using the AD7755 evaluation board. The current transducer used in this example is a shunt (400  $\mu\Omega$ ). The meter is intended to be used with a line voltage of 220 V and a maximum current of 25 A. The frequency outputs F1 and F2 can be used to drive a mechanical counter. These outputs will be calibrated to provide 100 imp/kWhr. The logic output CF has an output frequency that can be up to 128 times higher than the frequency on F1 and F2. This output can be used for calibration purposes and is shown connected to a frequency counter via the optoisolator in Figure 7.

At maximum current (25 A), the power seen by the meter will be 5.5 kW. This will produce a frequency of 0.153 Hz on F1 and F2 when these outputs are calibrated to 100imp/kWhr (100imp/hr = 0.02777 Hz,  $0.02777 \times 5.5 = 0.153 \text{ Hz}$ ). From Table III in the AD7755 data sheet, the closest frequency to 0.153 Hz in the half-scale ac inputs column is for F<sub>2</sub>, i.e., 0.17 Hz. Therefore F<sub>2</sub> is selected by setting S0 = 1 and S1 = 0. The choice of CF frequencies in this mode (see Table IV in the AD7755 data sheet) are 32 times F1 and 64 times F1. For this example 64 times F1 is selected by setting SCF = 1.

Since the voltage on Channel 1 is fixed, the only possible way of calibrating (adjusting) the output frequency in F1 and F2 is by varying the voltage on Channel 2. This is carried out by varying the attenuation of the line voltage using the trim pot.

First we can calculate the voltage required in Channel 2 in order to calibrate the frequency on the logic outputs F1 and F2 to 100imp/kWhr. The AD7755 data sheet gives the equation which relates the voltage on Channel 1 and Channel 2 to the output frequency on F1 and F2.

$$Freq = \frac{8.06 \times V1 \times V2 \times Gain \times F_{1-4}}{V_{PEF}^{2}}$$

(1)

First a current is selected for calibration, 5 A for example. This gives a Channel 1 voltage of  $400\,\mu\Omega\times5$  A = 2 mV rms. The gain of Channel 1 on the AD7755 is set to 16 (G0 = G1 = 1). The on-chip or external reference of 2.5 V is selected using JP13.

The output frequency at 5 A on F1 and F2 should be 0.02777 Hz (100imp/kWhr) × 1.1 (220 V × 5 A = 1.1 kW) = 0.03055 Hz.

From Equation 1 the voltage on Channel 2 should be set to 218 mV. The attenuation network as shown in Figure 1 is used to attenuate 220 V to 218 mV. R53 = 660 k $\Omega$ , R54 = 100 k $\Omega$ , R56 = 500  $\Omega$  and the trim pot R31 = 500  $\Omega$ .

However, since the meter is being calibrated at CF and CF is set to 64 times F1, the voltage on Channel 2 should be adjusted until CF =  $64 \times 0.03055$  Hz = 1.9555 Hz is registered on the frequency counter. The counter should be set up to display the average of ten frequency measurements on CF. This will remove any ripple due to the instantaneous power signal. See the AD7755 data sheet for more details.

-4- REV. 0

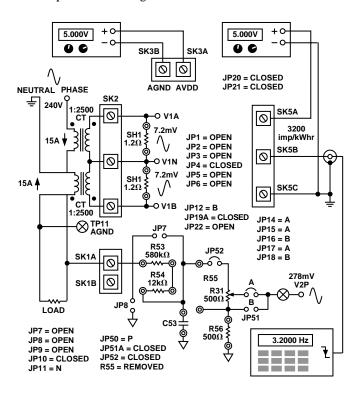

# AD7751 EVALUATION BOARD SET UP AS AN ENERGY METER

Figure 8 shows a wiring diagram that allows a simple energy meter to be implemented using the AD7751 evaluation board. Because the AD7751 monitors both the phase and neutral currents, isolation is required on at least one of the current transducers. One convenient way to provide isolation and eliminate problems with matching is to use two CTs (current transformers). The CTs are connected as shown in Figure 8. The CTs have a turns ratio of 1:2500. The burden resistance for the CTs can be placed on the evaluation board at SH1 and SH2. The meter is intended to be used with a line voltage of 240 V and a maximum current of 60 A. The frequency outputs F1 and F2 can be used to drive a mechanical counter. These outputs will be calibrated to provide 100 imp/kWhr. The logic output CF has an output frequency that can be up to 128 times higher than the frequency on F1 and F2. This output can be used for calibration purposes and is shown connected to a frequency counter via the optoisolator in Figure 8.

Figure 8. AD7751 Evaluation Board as an Energy Meter

At maximum current (60 A) the power see by the meter will be 14.4 kW. This will produce a frequency of 0.4 Hz on the logic outputs F1 and F2 when these outputs are calibrated to 100imp/kWhr (100imp/hr = 0.02777 Hz, 0.02777  $\times$  14.4 = 0.4 Hz). From Table III in the AD7751 data sheet, the closest frequency to 0.4 Hz in the half-scale ac inputs column is for F<sub>3</sub>, i.e., 0.34 Hz. Therefore F<sub>3</sub> is selected by setting S0 = 0 and S1 = 1. The choice of CF frequencies in this mode (see Table IV in the AD7751 data sheet) are 16 times F1 and 32 times F1. For this example 32 times F1 is selected by setting SCF = 1.

Since the voltage on Channel 1 is fixed, the only possible way of calibrating (adjusting) the output frequency on F1 and F2 is by varying the voltage on Channel 2. This is carried out by varying the attenuation of the line voltage using the trim pot.

First we can calculate the voltage required on Channel 2 in order to calibrate the frequency on F1 and F2 to 100imp/kWhr. The AD7751 data sheet gives the equation which relates the voltage on Channel 1 and Channel 2 to the output frequency on F1 and F2.

$$Freq = \frac{5.74 \times V1 \times V2 \times Gain \times F_{1-4}}{V_{REF}^{2}}$$

(2)

First a current is selected for calibration, 15 A for example. This gives a Channel 1 voltage of 15 A/2500  $\times$  1.2  $\Omega$  = 7.2 mV rms. The gain of Channel 1 on the AD7755 is set to 8 (G0 = 0, G1 = 1). The on-chip or external reference of 2.5 V is selected using IP13.

The output frequency at 15 A on F1 and F2 should be  $0.02777 \text{ Hz} (100 \text{imp/kWhr}) \times 3.6 (240 \text{ V} \times 15 \text{ A} = 3.6 \text{ kW}) = 0.1 \text{ Hz}.$

From Equation 2 the voltage on Channel 2 should be set to 278 mV. The attenuation network as shown in Figure 1 is used to attenuate 240 V to 278 mV. R53 = 580 k $\Omega$ , R54 = 12 k $\Omega$ , R56 = 500  $\Omega$  and the trim pot R31 = 500  $\Omega$ .

However since the meter is being calibrated at CF and CF is set to 32 times F1, the voltage on Channel 2 should be adjusted until CF =  $32 \times 0.1$  Hz = 3.2 Hz is registered on the frequency counter. The counter should be set up to display the average of ten frequency measurements on CF. This will remove any ripple due to the instantaneous power signal. See the AD7751 data sheet for more details.

REV. 0 \_5\_

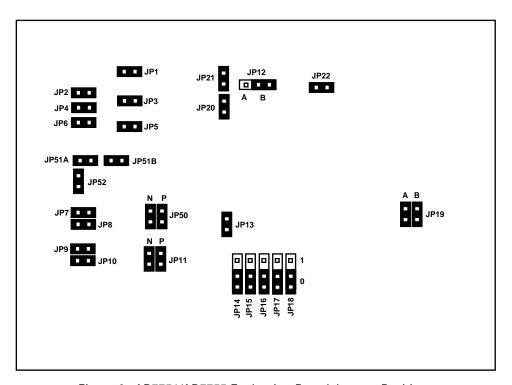

#### **JUMPER SELECTION**

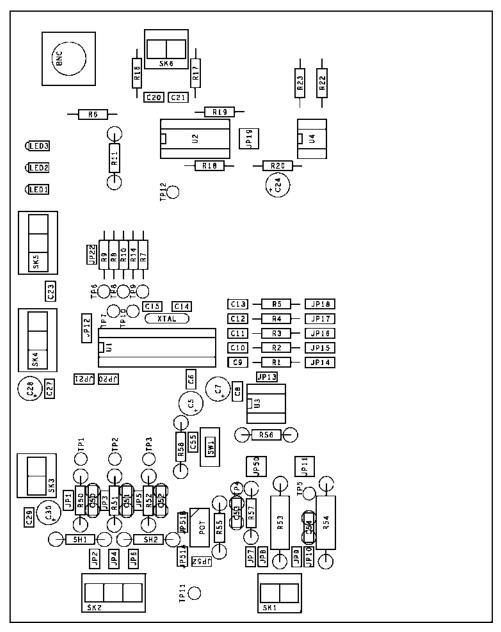

The AD7751/AD7755 evaluation board comes with several jumper selections that allow the user to exercise all of the AD7751 and AD7755 functionality. There are also some options such as attenuation networks and optically isolated outputs that allow the AD7751 and AD7755 to be evaluated under the same conditions as the end application. Table I outlines all the jumper options and explains how they are used. Table I should be used in conjugation with Figure 9, which will make it easier to locate the jumper in question.

Table I.

| Jumper | Option | Description                                                                                                                                                                                                                                                                        |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1    | Closed | Closing this jumper will short resistor R50 and connect analog input V1A directly to SK2A. This has the effect of removing the antialias filters from this input.                                                                                                                  |

|        | Open   | Antialias filter in input V1A is enabled.                                                                                                                                                                                                                                          |

| JP2    | Closed | Analog input V1A is connected to analog ground (AGND) via the antialias filter.                                                                                                                                                                                                    |

|        | Open   | Normal operation.                                                                                                                                                                                                                                                                  |

| JP3    | Closed | Closing this jumper will short resistor R51 and connect analog input V1N directly to SK2B. This has the effect of removing the antialias filters from this input.                                                                                                                  |

|        | Open   | Antialias filter in input V1A is enabled.                                                                                                                                                                                                                                          |

| JP4    | Closed | Analog input V1N is connected to analog ground (AGND) via the antialias filter. This jumper should be closed if the AD7751 is being used as these inputs are used single-ended on the AD7751.                                                                                      |

|        | Open   | When evaluating the AD7755, Channel 1 is best used in a differential mode and this jumper should be left open. An example is shown in Figure 4. In this example a shunt is used to sense the current. The shunt can be referenced to the AGND of the board by using TP11 as shown. |

| JP5    | Closed | Closing this jumper will short resistor R52 and connect analog input V1B (V1P AD7755) directly to SK2C. This has the effect of removing the antialias filters from this input.                                                                                                     |

|        | Open   | Antialias filter in input V1A (V1P) is enabled.                                                                                                                                                                                                                                    |

| JP6    | Closed | Analog input V1B (V1P) is connected to analog ground (AGND) via the antialias filter.                                                                                                                                                                                              |

|        | Open   | Normal operation.                                                                                                                                                                                                                                                                  |

| Jumper                                           | Option | Description                                                                                                                                                                                                                                                                                     |  |

|--------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JP7                                              | Closed | Closing this jumper will short resistors R53 and R54. The analog input V2P is connected directly to SK1A. This has the effect of removing the antialias filter and attenuation network from this input. Note: if the board is being connected to a high voltage, this jumper must be left open. |  |

|                                                  | Open   | Antialias filter and attenuation network on the input V2P is enabled.                                                                                                                                                                                                                           |  |

| ground (AGND) Note: SK1A is al and care should b |        | Analog input V1A is connected to analog ground (AGND) via the antialias filter.  Note: SK1A is also connected to AGND and care should be taken if this input is connected to a high voltage source.                                                                                             |  |

|                                                  | Open   | Normal operation.                                                                                                                                                                                                                                                                               |  |

| JP9                                              | Closed | Closing this jumper will short resistor R57 and connect analog input V2N directly to SK2B. This has the effect of removing the antialias filters from this input.                                                                                                                               |  |

|                                                  | Open   | Antialias filter in input V2N is enabled.                                                                                                                                                                                                                                                       |  |

| JP10                                             | Closed | Analog input V2N is connected to analog ground (AGND) via the antialias filter. This option should be selected if Channel 2 is being used in a single-ended mode.                                                                                                                               |  |

|                                                  | Open   | V2N connected to SK2B for differential operation.                                                                                                                                                                                                                                               |  |

| JP11                                             | N<br>P | SK1B connected to V2N (AD7751/AD7755).<br>SK1B connected to V2P (AD7751/                                                                                                                                                                                                                        |  |

|                                                  |        | AD7755).                                                                                                                                                                                                                                                                                        |  |

| JP12                                             | A      | Logic input $AD/\overline{DC}$ is connected to DGND.                                                                                                                                                                                                                                            |  |

|                                                  | В      | Logic input $AD/\overline{DC}$ is connected to DVDD.                                                                                                                                                                                                                                            |  |

| JP13                                             | Open   | AD7751/AD7755 internal (on-chip) reference selected.                                                                                                                                                                                                                                            |  |

|                                                  | Closed | External (AD780) reference selected.                                                                                                                                                                                                                                                            |  |

| JP14                                             | 1 0    | SCF connected to DVDD. SCF connected to DGND.                                                                                                                                                                                                                                                   |  |

|                                                  |        |                                                                                                                                                                                                                                                                                                 |  |

| JP15                                             | 0      | S1 connected to DVDD. S1 connected to DGND.                                                                                                                                                                                                                                                     |  |

| JP16                                             | 1      | S0 connected to DVDD.                                                                                                                                                                                                                                                                           |  |

|                                                  | 0      | S0 connected to DGND.                                                                                                                                                                                                                                                                           |  |

| JP17                                             | 1 0    | G1 connected to DVDD. G1 connected to DGND.                                                                                                                                                                                                                                                     |  |

| JP18                                             | 1 0    | G0 connected to DVDD. G0 connected to DGND.                                                                                                                                                                                                                                                     |  |

-6- REV. 0

| Jumper | Option | Description                                                                                                  | Jumper | Option | Description                                                                                                                                                              |

|--------|--------|--------------------------------------------------------------------------------------------------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP19   | A      | CF logic output connected to optically isolated output at SK5.                                               | JP51   | A      | Trim pot R31 is connected to V2P (depending on the position of JP50)—see Figure 1. This allows the AD7751/AD7755 output frequency to be scaled using the voltage on V2P. |

|        | В      | CF logic output connected to LED.                                                                            |        |        |                                                                                                                                                                          |

| JP20   | Closed | AVDD and DVDD connected together.                                                                            |        |        |                                                                                                                                                                          |

| JP21   | Closed | DVDD and VCC connected together.                                                                             |        | В      | When option B is selected, the jumper JP52                                                                                                                               |

| JP22   | Closed | Closed Output FAULT (NC on AD7755) is connected to DGND via R7. JP22 should be closed when using the AD7755. |        |        | should be left open. In this configuration the attenuation for V2P is provided via the fixed resistors R53, R54, R55 and R56.                                            |

| ,      | Open   | Should be open when evaluating the AD7751. Leaving closed will disable the FAULT LED.                        | JP52   | Open   | When open, the attenuation on V2P is provided by fixed resistor as explained above. Also see Figure 1.                                                                   |

| JP50   | N<br>P | SK1A connected to V2N (AD7751/<br>AD7755).<br>SK1A connected to V2P (AD7751/<br>AD7755).                     |        | Closed | When closed, the trim pot becomes part of the attenuation network. In this mode of operation the resistor R55 should be removed from its PCB jack sockets.               |

Figure 9. AD7751/AD7755 Evaluation Board Jumper Positions

REV. 0 -7-

#### **Evaluation Board Bill of Material**

| Designator                              | Value                                      | Description                                                                                                                                                                                                                                             |  |  |  |

|-----------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R1, R2, R3, R4, R5, R23                 | 1 kΩ, 5%, 1/4 W                            | Resistor, No Special Requirements.                                                                                                                                                                                                                      |  |  |  |

| R6, R22 100 Ω, 5%, 1/4 W                |                                            | Resistor, No Special Requirements.                                                                                                                                                                                                                      |  |  |  |

| R7, R8, R9, R10, R58                    | $10 \text{ k}\Omega$ , 5%, $1/4 \text{ W}$ | Resistor, No Special Requirements.                                                                                                                                                                                                                      |  |  |  |

| R11 51 Ω, 1%, 1/4 W                     |                                            | FARNELL Part No. 335-629. Not placed unless external clock is being used.                                                                                                                                                                               |  |  |  |

| R14, R18, R19, R20                      | 820 $\Omega$ , 5%, 1/4 W                   | Resistor, No Special Requirements.                                                                                                                                                                                                                      |  |  |  |

| R16, R17                                | $20 \Omega$ , 5%, $1/4 W$                  | Resistor, No Special Requirements.                                                                                                                                                                                                                      |  |  |  |

| R31 500 Ω, 10%, 1/2 W                   |                                            | Trim Pot Resistor, 25 Turn. BOURNS. FARNELL Part No. 348-247.                                                                                                                                                                                           |  |  |  |

| R50, R51, R52, R57 1 kΩ, 0.1%, 1/4 W    |                                            | ±15 ppm/°C Resistor, good tolerance, used as part of the analog filter network. These resistors are not soldered, but are plugged into PCB mount sockets for easy modification by the customer. Low drift WELWYN RC55 Series, FARNELL Part No. 339-179. |  |  |  |

| R53                                     | 1 M $\Omega$ , 10%, 0.6 W                  | ±50 ppm/°C, FARNELL Part No. 336-660.                                                                                                                                                                                                                   |  |  |  |

| R54                                     | 100 k $\Omega$ , 10%, 1/4 W                | ±15 ppm/°C, FARNELL Part No. 341-094.                                                                                                                                                                                                                   |  |  |  |

| R55, R56                                | 499 Ω, 0.1%, 1/4 W                         | ±15 ppm/°C Resistor, Good Tolerance. Low Drift. FARNELL Part No. 338-886.                                                                                                                                                                               |  |  |  |

| C5, C7, C24, C28, C30                   | 10 μF, 10 V dc                             | Power supply decoupling capacitors, 20%, Philips CW20C 104, FARNELL Part No. 643-579.                                                                                                                                                                   |  |  |  |

| C14, C15                                | 22 pF, Ceramic                             | Gate Oscillator Load Capacitors, FARNELL Part No. 108-927.                                                                                                                                                                                              |  |  |  |

| C6, C8, C27, C29, C23,<br>C20, C21, C55 | 100 nF, 50 V                               | Power Supply Decoupling Capacitors, 10%, X7R type, AVX-KYOCERNA, FARNELL Part No. 146-227.                                                                                                                                                              |  |  |  |

| C9, C10, C11, C12, C13                  | 10 nF                                      | Philips CW15C 103 M, FARNELL Part No. 146-224.                                                                                                                                                                                                          |  |  |  |

| C50, C51, C51, C53, C54                 | 33 nF, 10%, 50 Volt                        | X7R Capacitor, Part of the Filter Network. These resistors are not soldered, but are plugged into PCB mount sockets for easy modification by the customer. SR15 series AVX-KYOCERNA, FARNELL Part No. 108-948.                                          |  |  |  |

| U1                                      | AD7751 or AD7755                           | Supplied by Analog Devices Inc.                                                                                                                                                                                                                         |  |  |  |

| U2                                      | 74HC08                                     | Quad CMOS AND gates.                                                                                                                                                                                                                                    |  |  |  |

| U3                                      | AD780                                      | 2.5 V Reference, Supplied by Analog Devices Inc.                                                                                                                                                                                                        |  |  |  |

| U4                                      | H11L1                                      | Optical Isolator, by QT, FARNELL Part No. 326-896.                                                                                                                                                                                                      |  |  |  |

| D1, D2, D3                              | LED                                        | Low Current, Red, FARNELL Part No. 637-087.                                                                                                                                                                                                             |  |  |  |

| Y1                                      | 3.579545 MHz                               | Quartz Crystal, IQD A119C, 50 ppm/°C, FARNELL Part No. 170-229. HC49 Can Style, Pitch 4.88 mm.                                                                                                                                                          |  |  |  |

| SK1, SK3, SK6                           | Screw Terminal                             | 15 A, 2.5 mm Cable Screw Terminal Sockets. FARNELL Part No. 151-785. Length 10 mm, Pitch 5 mm, Pin diameter 1 mm.                                                                                                                                       |  |  |  |

| SK2, SK4, SK5                           | Screw Terminal                             | 15 A, 2.5 mm Cable Screw Terminal Sockets. FARNELL Part No. 151-786. Length 15 mm, Pitch 5 mm, Pin diameter 1 mm.                                                                                                                                       |  |  |  |

| BNC                                     | BNC Connector                              | Straight Square, 1.3 mm Holes, $10.2 \text{ mm} \times 10.2 \text{ mm}$ . FARNELL Part No. 149-453.                                                                                                                                                     |  |  |  |

-8- REV. 0

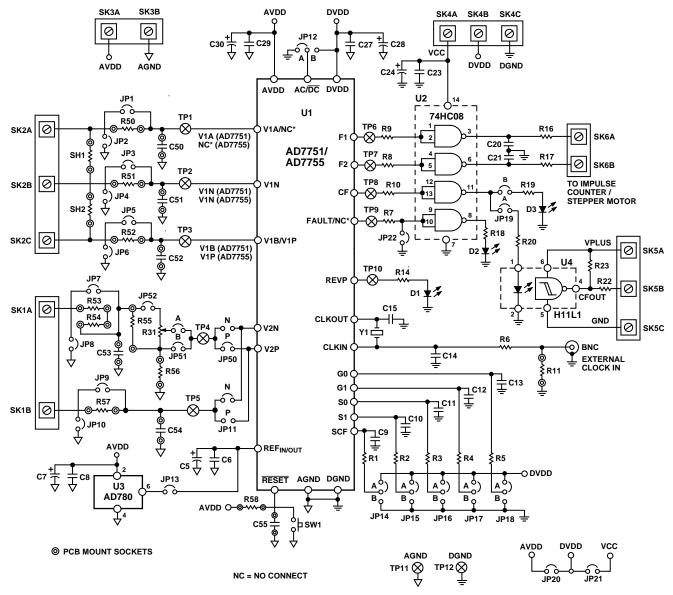

Figure 10. Evaluation Board Schematic

REV. 0 –9–

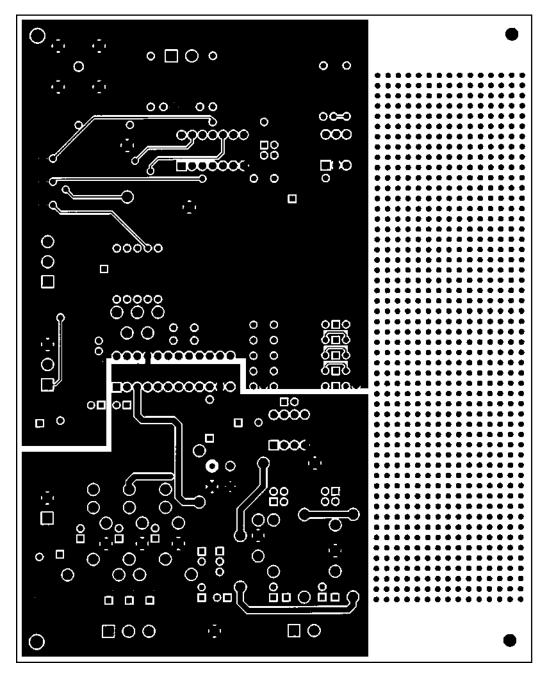

Figure 11. PCB Layout-Component Side

-10- REV. 0

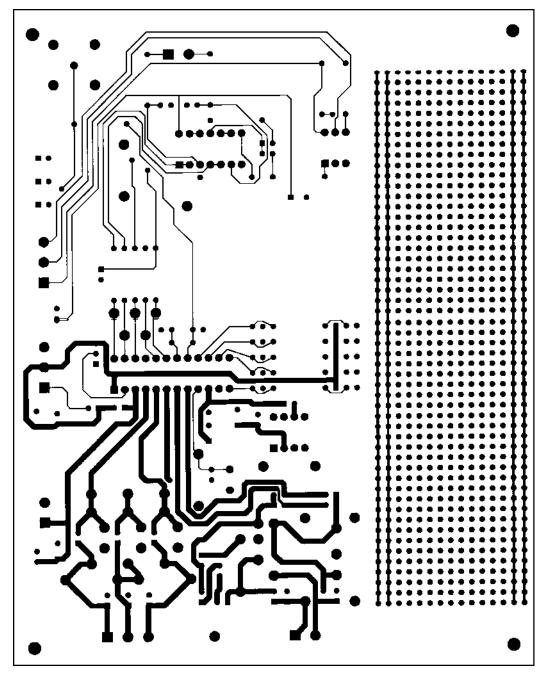

Figure 12. PCB Layout–Solder Side

REV. 0 -11-

Figure 13. PCB Layout-Component Placement